# Capacitor Voltages Measurement and Balancing in Flying Capacitor Multilevel Converters Utilizing a Single Voltage Sensor

Ghias Farivar, Student Member, IEEE, Amer M. Y. M. Ghias, Member, IEEE,Branislav Hredzak, Senior Member, IEEE, Josep Pou, Senior Member, IEEE,and Vassilios G. Agelidis, Fellow, IEEE

#### Abstract

This paper proposes a new method for measuring capacitor voltages in multilevel flying capacitor (FC) converters that requires only one voltage sensor per phase-leg. Multiple dc voltage sensors traditionally used to measure the capacitor voltages are replaced with a single voltage sensor at the ac-side of the phase-leg. The proposed method is subsequently used to balance the capacitor voltages using only the measured ac voltage. The operation of the proposed measurement and balacing method is independent of the number of the converter levels. Experimental results presented for a five-level FC converter verify effective operation of the proposed method.

## I. INTRODUCTION

Multilevel converters have attracted significant interest for medium/high power applications [1]–[3]. Among various multilevel converter topologies [4], the flying capacitor (FC) converter is one of the popular structures [5]–[10]. The FC converter [11] offers some advantages over the neutral-point-clamped (NPC) converter [12], such as that capacitor voltage balance can be

Manuscript received June 30, 2016.

The authors are with the Australian Energy Research Institute and the school of electrical engineering and telecommunication at the University of New South Wales (UNSW Australia), Sydney, NSW 2052 Australia (e-mails: g.farivar@unsw.edu.au, aghias@sharjah.ac.ae, b.hredzak@unsw.edu.au, j.pou@unsw.edu.au, vassilios.agelidis@unsw.edu.au).

achieved without producing low frequency voltage ripples in the FCs, even in converters with a large number of levels.

Phase-shifted pulse-width modulation (PS-PWM) is a common technique applied to FC converters, as it provides natural capacitor voltage balance. However, the quality of line-to-line voltages is not the best [13]. On the other hand, phase-disposition PWM (PD-PWM) produces better line-to-line voltages than PS-PWM, but it cannot be applied straightforward to the FC converter. Some solutions to produce PD-PWM are based on modifying the shapes of the carriers [14], [15]. However, each cell requires different carriers, which complicates its practical implementation, especially for FC converters with a large number of levels. The technique was simplified in [16], and the number of carriers was reduced from  $(n-1)^2$  to (n-1), *n* being the number of voltage levels. The main drawback is that it requires significant digital signal power processing. A similar kind of technique was proposed in [20] with the advantage of using only a single carrier.

The property of natural capacitor voltage balance in FC converters can be boosted by the addition of *RLC* filters connected to the output of the converter [17]–[20]. Closed-loop voltage balancing methods have also been reported in the technical literature [21]–[28]. However, the main disadvantage in those techniques is the use of multiple voltage sensors (one sensor per capacitor), which increases the system complexity and reduces reliability.

This paper proposes a new capacitor voltage measuring method that requires a single voltage sensor per phase-leg. The proposed measuring method is used to improve the balancing method discussed in [27] for multilevel FC converters. The proposed balancing method is simpler than the conventional one (based on using multiple voltage sensors) and requires only one voltage sensor. As in [27], the proposed method is able to maintain capacitor voltage balance and is very simple to implement in a digital signal processor.

The paper is organized as follows. Section II describes the operating principle of a FC converter and the PS-PWM technique. Section III introduces the proposed capacitor voltages measurement and balancing method based on a single sensor. Section IV presents experimental results obtained from a single-phase five-level FC converter. Finally, the conclusions are summarized in Section V.

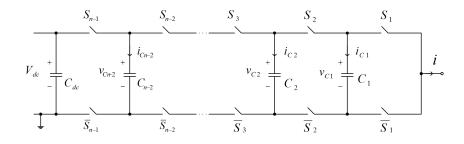

Fig. 1. Phase-leg of an n-level FLC Converter.

## II. FC CONVERTER AND PS-PWM

#### A. Fundamentals

Fig. 1 shows a phase-leg of an *n*-level FC converter, which integrates *n*-2 FCs. The switch pairs in the phase-leg  $s_1 - \bar{s}_1$ ,  $s_2 - \bar{s}_2$ ,..., and  $s_{n-1} - \bar{s}_{n-1}$  operate in a complementary manner. During normal operation, the mean voltage values of the FCs,  $C_1$ ,  $C_2$ ,..., and  $C_{n-2}$ , should be maintained at  $V_{dc}/(n-1)$ ,  $2V_{dc}/(n-1)$ ,..., and  $(n-2)V_{dc}/(n-1)$ , respectively, where  $V_{dc}$  is the dc-bus voltage. Consequently, the voltage across each switch is only 1/(n-1) of the dc-bus voltage. Each converter's phase-leg can generate *n* output voltage levels, i.e., 0,  $V_{dc}/(n-1)$ ,  $2V_{dc}/(n-1)$ ,...,  $(n-2)V_{dc}/(n-1)$ , and  $V_{dc}$ , with respect to the dc negative rail "0". Using Kirchhoff's voltage and current laws, the line-to-ground voltage, *v*, and the currents through the FCs can be written as:

$$v = s_{n-1}V_{dc} + \sum_{j=1}^{n-2} v_{cj}(s_j - s_{(j+1)})$$

(1)

$$i_{Cj} = (s_{j+1} - s_j)i,$$

(2)

for  $j = \{1, 2, ..., n - 2\}$ .

The control functions *s* represent the states of the upper switches, which take the values 0 or 1 when the corresponding switch is off or on, respectively.

# B. PS-PWM Technique

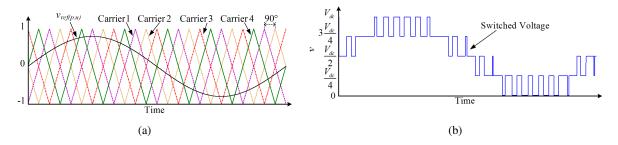

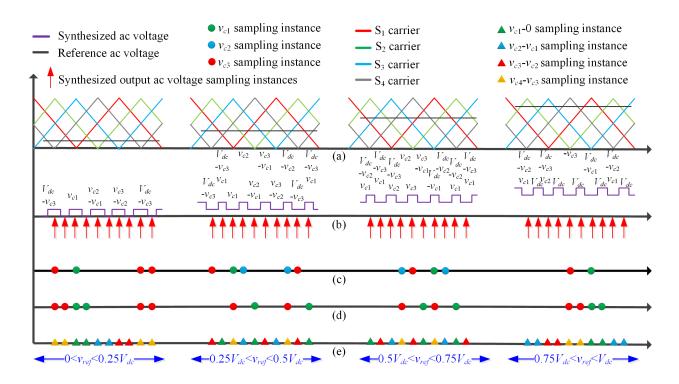

Fig. 2 shows the reference and carrier signals using a PS-PWM scheme applied to a five-level converter. In this converter, PS-PWM requires four carriers of the same amplitude and frequency, with a 90° phase-shift between consecutive carriers. A sinusoidal reference signal  $(v_{ref})$  that

Fig. 2. PS-PWM technique for a five-level converter: (a) reference sinusoidal signal with four triangular carriers and (b) switched phase voltage.

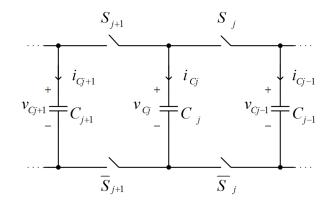

Fig. 3. A section of the FC chain.

ranges in the interval [-1, 1] under the linear modulation mode, is compared with all four triangular carriers to define the state of the switches. With this technique, each carrier is usually associated to a particular pair of switches. Using this method, natural voltage balancing can be achieved. However, this natural voltage balancing is usually slow and depends on the loading conditions. Therefore, an active balancing method is required to regulate the FC voltages at their desired levels with improved dynamics, especially under transient conditions and nonlinear loads.

The active voltage balancing method developed in [27], is based on the analysis of a generic cell section of the FC converter, as shown in Fig. 3. According to (2), the current through a capacitor is affected by the control signals associated with the two adjacent switches. The locally-averaged representation of the capacitor current in (2) calculated over a switching period

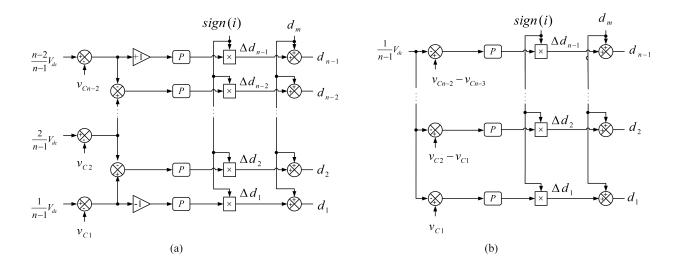

Fig. 4. a) Active voltage balancing method for a general *n*-level FC converter proposed in [27], b) Voltage balancing method for a general *n*-level FC converter proposed in this paper.

is:

$$\bar{i}_{Cj} = (d_{j+1} - d_j)\bar{i},\tag{3}$$

where  $\bar{i}_{Cj}$  and  $\bar{i}$  are the locally-averaged currents of the capacitor  $C_j$  and the output current, respectively, and  $d_{j+1}$  and  $d_j$  are the duty cycles of the switches  $s_{j+1}$  and  $s_j$ , respectively.

Assuming positive output current (i > 0), (3) shows that increasing the duty cycle  $d_{j+1}$  will increase the locally-averaged current through the capacitor, whereas the opposite effect will be produced if  $d_j$  is increased. If the voltage of the capacitor  $C_j$  is greater than its reference value, a negative current should be imposed to this capacitor. Therefore, the duty cycles  $d_j$  and  $d_{j+1}$  should be increased and decreased, respectively. On the other hand, if the output current is negative (i<0), the duty cycles should be manipulated in the opposite direction to help for voltage balance. Based on this analysis, the voltage balancing method shown in Fig. 4(a) was proposed in [27].

The voltage balancing dynamics of the capacitor  $C_j$  can be analyzed based on:

$$\frac{d\overline{v}_{Cj}}{dt} = \frac{i_{Cj}}{C_j}.$$

(4)

From (3) and (4), one can obtain:

$$\frac{d\overline{v}_{Cj}}{dt} = \frac{\overline{i}(d_{j+1} - d_j)}{C_j},\tag{5}$$

where,

$$d_{j+1} = d_m + \Delta d_{j+1},\tag{6}$$

$$d_i = d_m + \Delta d_i,\tag{7}$$

where  $d_m$  ranges in the interval [0,1] and is derived as follows:

$$d_m = \frac{v_{ref(p.u)} + 1}{2},$$

(8)

where,  $v_{ref(p.u)}$  is the normalized ac reference signal within the interval [-1, 1].

Assuming small variations around the operating point, using (6) and (7) in (5), one can obtain:

$$\frac{\Delta \overline{v}_{Cj}}{\Delta t} = \frac{\overline{i}(\Delta d_{j+1} - \Delta d_j)}{C_j}.$$

(9)

The variations of the duty cycles are given by a proportional controller, as follows:

$$\Delta d_{j+1} = sign(i)(\varepsilon_j - \varepsilon_{j+1})P, \tag{10}$$

$$\Delta d_j = sign(i)(\varepsilon_{j-1} - \varepsilon_j)P,\tag{11}$$

where  $\varepsilon_{j-1}$ ,  $\varepsilon_j$ , and  $\varepsilon_{j+1}$  are the voltage errors in the capacitors  $C_{j-1}$ ,  $C_j$ , and  $C_{j+1}$ , respectively, and P is the proportional control parameter. sign(i) is the sign of the output current defined as 1 and -1 when i is positive and negative, respectively. Substituting (10) and (11) into (9):

$$\frac{\Delta \overline{v}_{cj}}{\Delta t} = \frac{|\overline{i}| P(2\varepsilon_j - \varepsilon_{j+1} - \varepsilon_{j-1})}{C_j} \tag{12}$$

defines the balancing dynamic of the proposed voltage control and can be used to tune the controller gain parameter (P) to achieve a satisfactory system performance. This technique is very simple to implement on FC converters with any number of levels, as it just requires a proportional controller. However, the main drawback is the need for multiple dc voltage sensors.

# III. PROPOSED METHOD FOR MEASURING CAPACTIOR VOLTAGES AND PERFORMING VOLTAGE BALANCING

In this section, a method for capacitor voltages measurement and balancing in FC converters is described. The objective of the method is to measure and regulate all the capacitor voltages by only using the output voltage measurement, v. The relationship between the output voltage and the capacitor voltages is governed by the switching function shown in (1).

Fig. 5. (a) Carrier waveforms and reference signals for all possible voltage regions, (b) synthesized output voltage and number of conducting capacitors for each switching instance, (c) voltages sampling instances using the direct capacitor voltage measurement strategy, (d) voltages sampling instances using the indirect capacitor voltage measurement strategy, and (e) voltages sampling instances using the proposed measurement strategy.

There are two general strategies proposed in the literature to reconstruct the capacitor voltages of multilevel converters by sensing the ac output voltage. In the first strategy, the capacitor voltages are measured directly when there is only one capacitor conducting. The shortcoming of this approach is that it fails to provide measurement for the switching instances where several capacitors contribute to build the output voltage. Therefore, the chance of measuring the capacitor voltages is limited, especially in converters with high number of levels. For the switching instances in which multiple capacitors are conducting, an estimation mechanism needs to be implemented to provide the voltage feedback signal for the controller.

The second strategy, on the other hand, does not rely on the direct measurement. It monitors the voltage steps on the output voltage and therefore, measures the voltage of the capacitor that produced the step. This strategy provides a measurement at each switching instance for modular converters with equal capacitor voltages such as cascaded H-bridge (CHB) converter. However, the shortcoming of this strategy is that it does not provide a measurement when several capacitors switch at the same time to generate the voltage step. This situation happens most of the times in the FC converter as the voltage steps are generated by simultaneous switching of two adjacent capacitors, as it can be seen from (1). Therefore, in this strategy only  $v_{C1}$ , and if  $V_{dc}$  is known,  $v_{n-2}$  as well can be measured, and the rest of the capacitor voltages need to be estimated or measured individually.

Therefore, none of the abovementioned strategies are suitable for the FC converter. The objective is to provide the converter controller with capacitor voltages measured at a constant sampling frequency. In order to achieve this goal, (1) is rewritten as:

$$v = \sum_{j=1}^{n-1} (v_{Cj} - v_{Cj-1}) s_j$$

(13)

with  $v_{C0} = 0$  and  $v_{C(n-1)} = V_{dc}$ .

From (13), it can be seen that after each switching instance when  $s_j$  changes,  $v_{Cj} - v_{Cj-1}$  can be measured indirectly from:

$$v_{Cj} - v_{Cj-1} = |\frac{v' - v''}{s'_j - s''_j}|,\tag{14}$$

where, v' and s' are the quantities before the transition (output voltage step) and v'' and s'' are values after the transition. This is equivalent to measuring capacitor voltages in a CHB converter using the second strategy.

The active capacitors voltage balancing method discussed in Section II-B and shown in Fig. 4(a) uses the capacitor voltages as direct feedback. Using the new variables, the control system can be redrawn in a much simpler form as shown in Fig. 4(b).

Fig. 5 shows an example for a five-level converter. In this case, there are four regions where the reference signal can be located in:  $0 < v_{ref} < 0.25V_{dc}$ ,  $0.25V_{dc} < v_{ref} < 0.5V_{dc}$ ,  $0.5V_{dc} < v_{ref} < 0.75V_{dc}$ , and  $0.75V_{dc} < v_{ref} < V_{dc}$ . Four different examples are shown that correspond to operation in each of these voltage regions.

The triangular carriers and the reference waveform are shown in Fig. 5(a). The synthesized output voltage and the sampling instances are shown in Fig. 5(b). The sampling instances are synchronized with the carriers. A measurement will happen when a carrier reaches its peak or minimum. Therefore, a measurement is produced after each switching transition at the center of each pulse. The inserted capacitors that generate each pulse are also indicated.

The sampling instances at which a capacitor voltage can be measured using the first method (direct measurement) are depicted in Fig. 5(c). Similarly, the capacitor voltages measurable using the second method (indirect measurement) for each sampling instance are shown in Fig. 5(d). As it can be seen, none of these methods can provide measurement with constant sampling frequency and the chance of measuring a capacitor voltage is limited to specific instances.

Conversely, using the proposed measurement strategy, measurements take place at each sampling instance as shown in Fig. 5(e). Here, as it can be seen for each carrier period, all the control variables are updated twice per carrier period, which provides the controller with a high resolution constant frequency feedback signal.

The generated ac voltage undergoes a short transient after each voltage step due to parasitic capacitances and inductances. In the proposed measurement strategy the measurement happens at the center of pulse which allows sufficient time for the decay of transient oscillation. Hence, the measurement remains immune to these switching transients. However, when the pulse width is too narrow, there is not enough time for the output voltage to reach steady state before measurement. In this case, the measurement is not reliable and the measurement unit disregards it. When, no measurement is performed at a particular sampling instance, the previously measured capacitor voltages values are used in the control system. Similarly, in the over modulation region in which no pulse occurs in the output voltage, the previously measured capacitor voltages values are used. Since the resolution of the proposed capacitor voltages reconstruction method is high and the capacitor voltages cannot change abruptly, the assumption of using previously measured capacitor voltages does not deteriorate the performance of the system.

The chance of having a narrow pulse increases as the switching frequency increases. Similarly, if the number of converter levels increases the pulses become narrower. Therefore, even though the proposed method is, in theory, independent of the switching frequency and number of converter levels, in practice they will be limiting factors to achieve satisfactory performance.

It is worthwhile mentioning this limitation does not devaluate the proposed measurement strategy compared to the previously discussed methods as they suffer from the same limitation.

# **IV. EXPERIMENTAL RESULTS**

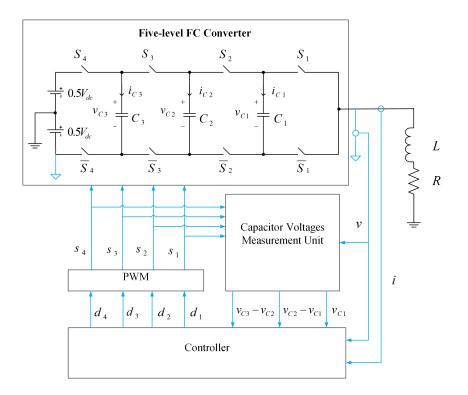

Experimental tests were performed on a low-power five-level FC converter. The circuit diagram of the converter prototype is shown in Fig. 6. The converter was controlled by a DSPACE 1006

Fig. 6. Circuit diagram of the experimental system.

| PARAMETERS OF THE EXPERIMENTAL PROTOTYPI |                                  |

|------------------------------------------|----------------------------------|

| Circuit Parameter                        | Value                            |

| Dc Bus Voltage, $V_{dc}$                 | 200 V                            |

| FCs $(C_1, C_2, C_3)$                    | 260 μF                           |

| Linear Load, RL                          | $R=10 \Omega$ , $L=6 \text{ mH}$ |

| Carrier Frequency, $f_s$                 | 500 Hz                           |

| Fundamental Frequency, f                 | 50 Hz                            |

TABLE I

PARAMETERS OF THE EXPERIMENTAL PROTOTYPE

with integrated DS 5203 FPGA board. The parameters of the converter are given in Table I.

The following three experiments were performed to compare the performance of the proposed single voltage sensor control system with the conventional one that uses as many voltage sensors as capacitors.

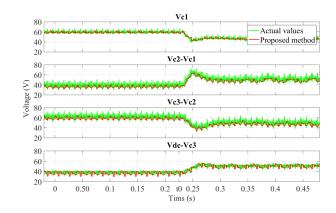

In the first experiment, initially, the capacitor voltage balancing method was deactivated and the voltages were regulated using natural PS-PWM. At time  $t_0$ , the proposed balancing method

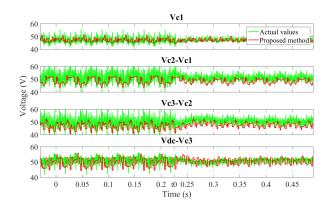

Fig. 7. Measured controllers' feedback signals using the proposed single voltage sensor method and using multiple voltage sensors (actual values) during a sudden balancing method activation test.

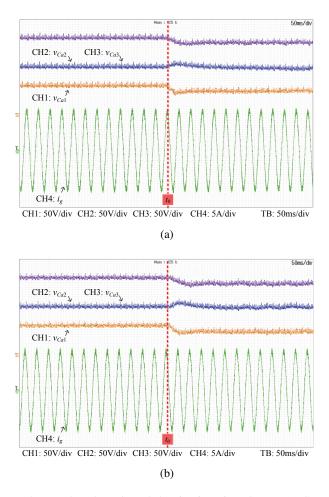

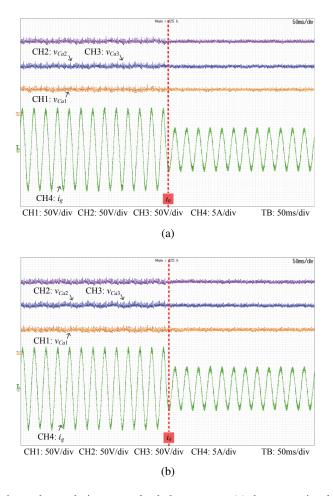

was activated to compensate the steady state error of the natural balancing and push the voltages towards the required reference values. The performance of the proposed single voltage sensor measurement method during this transient is shown in Fig. 7. As it can be seen, the proposed measurement method was able to track the actual values with high accuracy. In Fig. 8, the performance of the proposed and conventional balancing method [27] is compared. From these results, it can be concluded that with the proposed method the performance of the system does not deteriorate despite having simpler structure and lower sensor count.

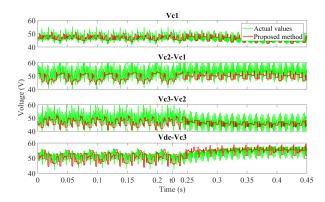

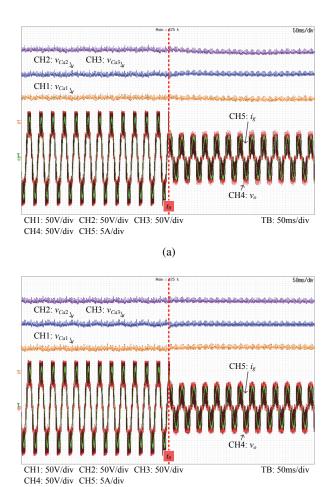

In the second experiment, the performance of the proposed method was tested against a sudden load transient. Initially, the converter was operated with the RL load given in Table I, then, at time  $t_0$ , the load was changed from  $R = 10\Omega$  to  $R = 20\Omega$ . Fig. 9 shows the effectiveness of the proposed single voltage sensor measurment method for this case. The dynamic performance of the proposed and conventional balancing method [27] is compared in Fig. 10(b). It can be seen that the proposed single voltage sensor method was able to regulate the capacitor voltages without any deterioration in the performance when compared with the conventional method.

In the last experiment, a step change in the amplitude of the ac voltage reference of the inverter from 0.9 p.u to 0.5 p.u was tested (base voltage,  $V_b=100$  V). The converter was operating with the *RL* load given in Table I. At time  $t_0$ , the modulation index *m* was changed from 0.9 to 0.5. Fig. 11 shows that the proposed measurement method can follow the actual voltages during this transient. The dynamic performance of the proposed and conventional balancing method [27] is compared in Fig. 12(a) and (b), respectively. No deterioration in performance can be observed when the

Fig. 8. Comparison of capacitor voltages when the voltage balancing is activated at  $t_0$ . (a) Conventional balancing method [27] and (b) proposed single voltage sensor balancing method.

Fig. 9. Measured controllers' feedback signals using the proposed single voltage sensor measurement method and using multiple voltage sensors (actual values) during a step load change at  $t_0$ .

Fig. 10. Comparison of capacitor voltages during a step load change at  $t_0$ : (a) the conventional balancing method in [27] and (b) the proposed balancing method.

proposed method based on a single voltage sensor was used. The experiments showed that the proposed single voltage sensor measurement and balancing method has equivalent performance in regulating the capacitor voltages as the conventional one. Additional results in Fig. 13 show that the load current quality remains unaffected as well. Fig. 13(a) shows the harmonic content of the load current when the conventional method is used. Comparing this figure with Fig. 13(b), which shows the harmonic content of the load current using the proposed method, it can be seen that the total harmonic distortion and the location and amplitude of the significant harmonics remain almost the same.

Fig. 11. Measured controllers' feedback signals using the proposed single voltage sensor measurement method and using multiple voltage sensors (actual values) during a step change in the ac reference voltage at  $t_0$ .

Fig. 12. Comparison of capacitor voltages during a step change in the ac reference voltage at  $t_0$ : (a) the conventional balancing method [27] and (b) the proposed balancing method.

(b)

Fig. 13. (a) Load current harmonics using the conventional method [27] and (b) the proposed method.

# V. CONCLUSION

This paper has proposed a new capacitor voltage measurement and balancing method for the FC converter, which allows effective operation when the capacitor voltage sensors are replaced with a single voltage sensor at the ac side. Effectiveness of the proposed method has been verified experimentally in a five-level FC converter prototype. The method is very simple to implement and can be applied to FC converters with different number of levels.

# REFERENCES

- [1] V. Yaramasu, B. Wu, and J. Chen, "Model-predictive control of grid-tied four-level diode-clamped inverters for high-power wind energy conversion," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2861-2873, Jun. 2014.

- [2] T. Freddy, N. A. Rahim, W. P. Hew, and H. S. Che, "Comparison and analysis of single-phase transformerless grid-connected PV inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5358-5369, Oct. 2014.

- [3] V. Yaramasu and B. Wu, "Predictive control of a three-level boost converter and an NPC inverter for high-power PMSGbased medium voltage wind energy conversion systems," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5308-5322, Oct. 2014.

- [4] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Fraquelo, B. Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial application of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553-2580, Jun. 2010.

- [5] A. K. Sadigh, V. Dargahi and K. A. Corzine, "Analytical Determination of Conduction and Switching Power Losses in Flying-Capacitor-Based Active Neutral-Point-Clamped Multilevel Converter," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5473-5494, Aug. 2016.

- [6] R. Naderi, A. K. Sadigh and K. M. Smedley, "Dual Flying Capacitor Active-Neutral-Point-Clamped Multilevel Converter," *IEEE Trans. Power Electron.*, vol. 31, no. 9, pp. 6476-6484, Sept. 2016.

- [7] K. Antoniewicz; M. Jasinski; M. Kazmierkowski; M. Malinowski, "Model Predictive Control for 3-Level 4-Leg Flying Capacitor Converter Operating as Shunt Active Power Filter," *IEEE Trans. Ind. Electron.*, (Early Access).

- [8] J. Amini, A. H. Viki, A. Radan and M. Moallem, "A General Active Capacitor Voltage Regulating Method for L-Level M-Cell N-Phase Flying Capacitor Multilevel Inverter With Arbitrary DC Voltage Distribution," *IEEE Trans. Ind. Electron.*, vol. 63, no. 5, pp. 2659-2668, May 2016.

- [9] F. Salinas, M. A. Gonzlez, M. F. Escalante and J. de Len Morales, "Control Design Strategy for Flying Capacitor Multilevel Converters Based on Petri Nets," *IEEE Trans. Ind. Electron.*, vol. 63, no. 3, pp. 1728-1736, March 2016.

- [10] P. R. Kumar, R. S. Kaarthik, K. Gopakumar, J. I. Leon and L. G. Franquelo, "Seventeen-Level Inverter Formed by Cascading Flying Capacitor and Floating Capacitor H-Bridges," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3471-3478, July 2015.

- [11] T. A. Meynard and H. Foch, "Multi-level conversion: High voltage choppers and voltage-source inverters," in *Proc. IEEE PESC*, 29 Jun.–3 Jul. 1992, vol. 1, pp. 397–403.

- [12] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA–17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [13] A. M. Y. M. Ghias, J. Pou, G. J. Capella, P. Acuna and V. G. Agelidis, "On Improving Phase-Shifted PWM for Flying Capacitor Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5384-5388, Aug. 2016.

- [14] S. Lee, D. Kang, Y. Lee, and D. Hyun, "The carrier-based PWM method for voltage balance of flying capacitor multilevel converter," in *Proc. IEEE PESC*, Jun. 2001, vol.1, pp. 126–131.

- [15] D. W. Kang, B. K. Lee, J. H. Jeon, T. J. Kim, and D. S. Hyun, "A symmetric carrier technique of CRPWM for voltage balance method of flying-capacitor multilevel inverter," *IEEE Trans. Ind. Electron.*, vol. 52, no. 3, pp. 879–888, Jun. 2005.

- [16] A. Shukla, A. Ghosh, and A. Joshi, "Natural balancing of flying capacitor voltages in multicell inverter under PD carrierbased PWM," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1682–1693, Jun. 2011.

- [17] B. P. Mcgrath and D. G. Holmes, "Enhanced voltage balancing of a flying capacitor multilevel converter using phase (PD) modulation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1933–1942, Jul. 2011.

- [18] B.P. Mcgrath and D. G. Holmes, "Analytical determination of the capacitor voltage balancing dynamics for three phase flying capacitor converters," *IEEE Trans. Ind. Appl.*, vol. 45, no. 4, pp. 1425–1433, Jul. 2009.

- [19] B.P. Mcgrath and D. G. Holmes, "Natural capacitor voltage balancing for a flying capacitor converter induction motor drive," *IEEE Trans. Power Electron.*, vol. 24, pp. 1554–1561, Jun. 2009.

- [20] A. M. Y. M. Ghias, J. Pou, G. J. Capella, V. G. Agelidis, R. P. Aguilera, and T. Meynard, "Single-carrier phase-disposition PWM implementation for multilevel flying capacitor converters," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5376-5380, Oct. 2015.

- [21] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Improved natural balancing with modified phase-shifted

PWM for single-leg five-level flying-capacitor converters," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1658–1667, Apr. 2012.

- [22] G. Gateau, M. Fadel, P. Maussion, R. Bensaid, and T. A. Meynard, "Multicell converters: Active control and observation of flying capacitor voltages," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 998–1008, Oct. 2002.

- [23] C. Feng, J. Liang, and V. G. Agelidis, "Modified phase-shifted PWM control for flying capacitor multilevel converters," *IEEE Trans. Power Electron.*, vol. 22, pp. 178–185, Jan. 2007.

- [24] S. Choi and M. Saeedifard, "Capacitor voltage balancing of flying capacitor multilevel converters by space vector PWM," *IEEE Trans. Power Del.*, vol. 27, no. 3, pp. 1154–1161, Jul. 2012.

- [25] M. Khazraei, H. Sepahvand, K. A. Corzine, and M. Ferdowsi, "Active capacitor voltage balancing in single-phase flyingcapacitor multilevel power converters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 769–778, Feb. 2012.

- [26] A. M. Y. M. Ghias, J. Pou, V. G. Agelidis, and M. Ciobotaru, "Optimal switching transition-based voltage balancing method for flying capacitor multilevel converters," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 1804-1817, Apr. 2015.

- [27] A. M. Y. M. Ghias, J. Pou, M. Ciobotaru, and V. G. Agelidis, "Voltage balancing method using phase-shifted PWM for the flying capacitor multilevel converter," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4521-4531, Sep. 2014.

- [28] A. M. Y. M. Ghias, J. Pou, M. Ciobotaru, and V. G. Agelidis, "Voltage balancing method for a flying capacitor multilevel converter using phase disposition PWM," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6538–6546, Dec. 2014.